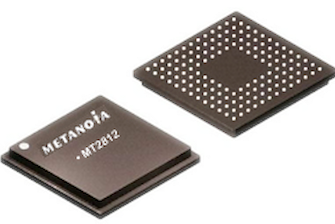

產品總覽

Metanoia’s MT2812 is a System on a Chip (SoC) that supports a wide range of wireless applications by converting multiple data formats to Ethernet medium. With a programmable modem that uses advanced DSP technology, dual RISC processors and integrated high speed data convertors, the MT2812 is ideal for converting packetized data to arbitrary wireless communication formats including 5G New Radio (5G NR).

The MT2812 SoC can be combined with the MT3812, Metanoia sub-6GHz RF transceivers and RF front end modules to build compact and highly flexible sub-6GHz 5G-NR Radio Units (RUs) systems. With most of the necessary building blocks provided by Metanoia, it is the most cost-effective and competitive solution to meet the needs of various market segments and operators in 5G network deployment.

產品應用

The MT2812 SoC supports a scalable architecture which can help in building higher density applications by using multiple instances of the chip.

Target Market Segments

Sub-6GHz low density O-RAN RU market (1T1R up to 4T4R Low density RU)

Complete end-to-end solution for 5G RU, including Digital Front-End (DFE) for Low-PHY, fronthaul interface as specified by O-RAN and also interface to sub-6GHz RF chip like Metanoia MT3812.

產品規格

| Two CPU Complex |

- e200z7 Core running up-to 625 MHz

- 32-bit PowerPC Book E compliant

- 64 kB Local Data Memory

- 16 kB Instruction Cache

- 16 kB Data Cache

- Memory Protection Unit (MPU) with 24-entry descriptor table

- Embedded Floating-point APU (EFPU2) supporting scalar and SIMD single-precision floating-point operations

- Signal Processing Extension (SPE2) APU supporting SIMD fixed-point operations, using the 64-bit General Purpose Register file

- Performance Monitor APU supporting execution profiling

|

| Tree VSPA3 16SP Complexes |

- 16 Complex 32-bit float mac per cycle

- 64 Real 32-bit float mac per cycle

- 32 Complex 24-bit float mac per cycle

- 28 Real 24-bit float mac per cycle

- Special Arithmetic Unit (SAU)

- Forward Error Correction Unit

- 128 kB VCPU and 192 kB IPPU Data Memory

- DMA

|

| 2 MB On-Chip SRAM |

| High DMA with CRC |

| Security Offload |

AES-256 crypto up to 2 Gbps |

| Interfaces |

- Integrated data converters 2T2R @ 100 MHz

- Up to 424 MSPS ADC x4 (RXI1, RXQ1, RXI2, RXQ2). Each pair of ADCs can be interleaved to give 848 MSPS effective

- Up to 848 MSPS DAC x4 (TXI1, TXQ1, TXI2, TXQ2)

- Timer outputs

- I2C Master and slave modes supported

- SPI interface with 2 Chip Selects

- FlexSPI supporting x4 serial NOR or NAND flash with 1 Chip Select

- GPIO

- 62550 Compatible 2-pin UART for debug console interface

- Light-Weight LVDS communication protocol

|

| Network I/O |

- 5 Gbps SGMII / SerDes and RGMII

- Ethernet management Interface

- IEEE 1588

|

| Standard 5-pin JTAG |

| Time Base Generator |

- 64-bit master counter

- Timing generation with timing advance and delay compensation

|

| Other Features |

- Absolute +/- 10% maximum rating core and I/O voltage

- Supply voltages: 1.8 V,1.2 V, 0.9 V, 0.8 V

- Operating Temperature between -40 °C (Ta) ~ 105 °C (Tj)

- ESD Criteria – HBM with 2000 V with test method for ESD per MIL-STD-883G Method 3015.7

- ESD Criteria – CDM with 500 V with test method for ESD per JESD22-C101-D.

- Latch up with 200 mA tolerance with test is based on JEDEC STANDARD EIA/JESD

|

| 16 nm FinFET technology, power consumption < 2.5 W, 8×8 mm FC-PBGA 164-pin package |

*Metanoia Authorized Distributor