How to use high-performance timing solutions to improve the large computing efficiency

By James Wilson, Senior Marketing Director, Timing Products, Silicon Labs

Learn more about Si538x, Si539x

Ethernet has come a long way since IEEE 802.3 was first published in 1980. First envisioned as a technology to connect PCs and workstations, Ethernet has gradually evolved to become the networking technology of choice for a broad range of applications across enterprise computing, data center, wireless networks, telecommunications and industrial. Due to the ubiquity of Ethernet and the ever-decreasing cost of the hardware needed to support it, Ethernet is poised to continue gaining popularity in these applications. Some of the most interesting technology transformations are currently underway as 100G Ethernet is being adopted in data centers and wireless radio access networks. These migrations to high-speed optical Ethernet are driving the need for higher performance clock and frequency control products.

Data Centers

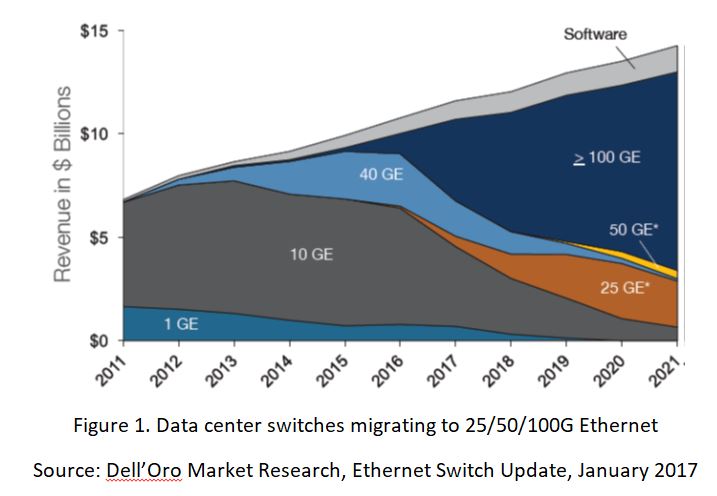

Traditional enterprise workloads are quickly migrating to public cloud infrastructure, driving a tremendous investment boom in data centers worldwide. In addition to increasing demands for lower latency, data centers share a unique challenge in that the majority of data center traffic stays within the data center as workload processing is distributed across multiple compute nodes. Modern data centers are optimizing their network architecture to support distributed, virtualized computing by connecting every switch to each other, a trend known as hyperscale computing. One of the underlying technologies that makes hyperscale computing commercially attractive is high-speed Ethernet. As the data in Figure 1 shows, data center switches are quickly migrating to 25G, 50G and 100G Ethernet to accelerate data transfer and network efficiency.

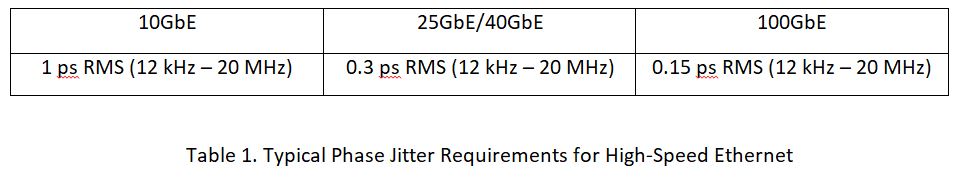

The migration from 10G to 25/50/100G Ethernet is driving data center equipment manufacturers to upgrade switch and access ports to higher speeds. This in turn fuels the need for higher performance, lower jitter timing solutions. Ultra-low jitter clocks and oscillators are necessary in these applications because high clock noise can result in unacceptably high bit-error rates or lost traffic. Table 1 highlights the typical timing requirements for Ethernet PHYs, switches and switch fabrics. The safe and proven approach for high-speed Ethernet is to use an ultra-low jitter clock source that delivers excellent jitter margin to these specifications.

Wireless Radio Access Networks

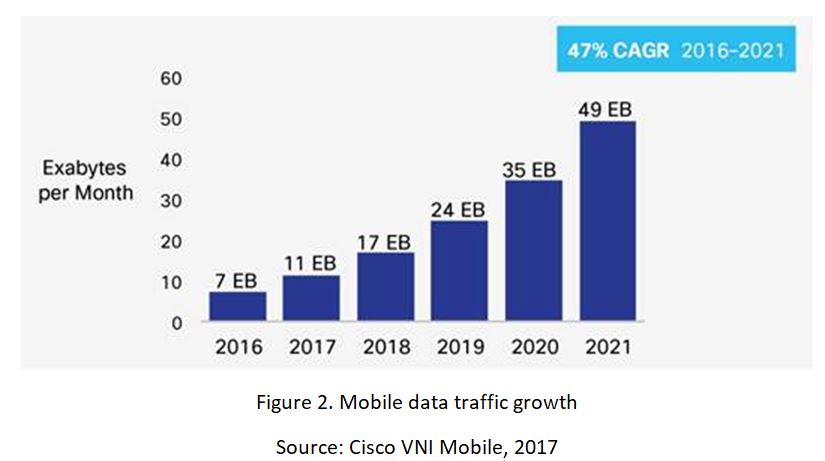

Wireless networks are poised to go through tremendous change as they migrate from 4G/LTE to LTE-Advanced and 5G over the next several years. Next-generation wireless networks will be optimized for carrying mobile data. As shown in Figure 2, mobile data traffic is expected to grow to 49 exabytes per month by 2021, a sevenfold increase over 2016. To support this exponential increase in demand for bandwidth, wireless networks are being re-architected and optimized for data transport. The widescale adoption of high-speed Ethernet in radio access networks (RAN) is expected to be a critical part of this technology advancement.

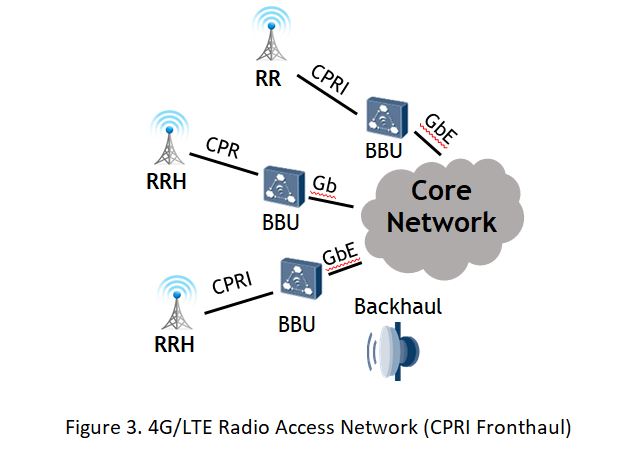

In 4G/LTE radio access networks, the RF and baseband processing functions performed by base stations are split into separate remote radio heads (RRH) and base band units (BBU). As shown in Figure 3, each RRH is connected to a BBU over a dedicated fiber connection based on the Common Public Radio Interface (CPRI) protocol. This architecture enables the replacement of dedicated copper and coax cable connections between the radio transceiver (typically located in the cell tower) and the base station (typically located at the ground nearby). This distributed architecture enables the BBU to be placed in a more convenient location to simplify deployment and maintenance. While more efficient than legacy 3G wireless networks, this network architecture is limited because the bandwidth is constrained by the speed of the CPRI link (typically 1 Gbps to 10 Gbps). In addition, the CPRI connection is a point-point link and RRH and BBUs are typically deployed in close proximity to each other (<2 km to 20 km), constraining the flexibility of network deployments.

As part of the evolution to 5G, the wireless industry is re-thinking base station architectures. The connection between baseband and radio elements, known as the fronthaul network, is a key area for optimization. Higher bandwidth fronthaul networks are required to support new LTE features that support high-speed mobile data, including Carrier Aggregration and Massive MIMO. In addition, network densification and the adoption of small cells, pico cells and micro cells will put additional bandwidth requirements on fronthaul networks. To minimize capex and opex, 5G will use a Cloud-RAN (C-RAN) architecture that centralizes baseband processing (C-BBU) for multiple remote radio heads.

New standards are being developed for fronthaul to support the evolution to C-RAN. IEEE 1904 Access Networks Working Group (ANWG) is developing a new Radio over Ethernet (RoE) standard for supporting CPRI encapsulation over Ethernet. This new standard will make it possible to aggregate CPRI traffic from multiple RRHs and small cells over a single RoE link, improving fronthaul network utilization. Another working group, IEEE 1914.1 Next Generation Fronthaul Interface (NGFI), is revisiting the Layer-1 partitioning between RF and baseband to support more Layer-1 processing at the RRH. NGFI enables the fronthaul interface to move from a point-to-point connection to a multipoint-to-multipoint topology, improving network flexibility and enabling better coordination between cell sites. A new CPRI standard for 5G front-haul (eCPRI) will be released in August 2017 that details the new functional partitioning of base station functions and includes support for CPRI over Ethernet.

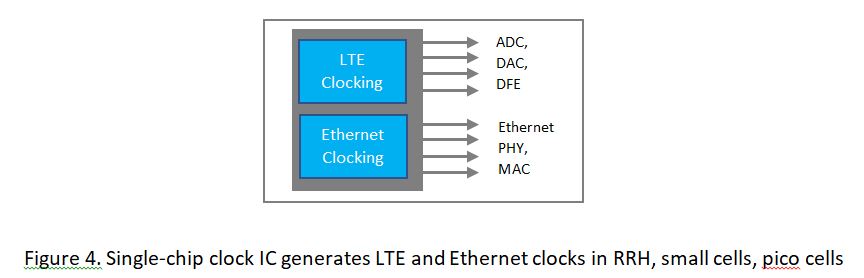

These new fronthaul standards create the need for frequency flexible timing solutions that can support both LTE and Ethernet clocking in radio heads, small cells, and pico cells, as shown in Figure 4. These new solutions provide the opportunity for hardware designs to unify all clock synthesis into a single, small-form factor IC.

Another key challenge is accurate timing and synchronization. Historically 3G and LTE-FDD mobile networks relied on frequency synchronization to synchronize all network elements to a very precise and accurate primary reference, typically sourced from a signal transmitted by GNSS satellite systems (GPS, BeiDou). These systems require frequency accuracy within 50 ppb at the radio interface and 16 ppb at the base station interface to the backhaul network. LTE-TDD and LTE-Advanced retain these frequency accuracy requirements but add very stringent phase synchronization requirements (+/-1.5 us). This is a key requirement to enable new features such as enhanced inter-cell interference coordination (eCIC) and coordinated multipoint (CoMP), which maximize signal quality and spectral efficiency. These phase synchronization requirements are expected to be further tightened in the upcoming 5G standards.

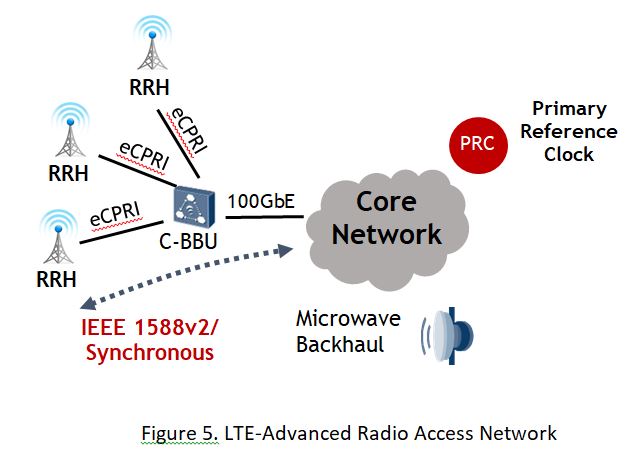

Figure 5 shows the LTE-Advanced network architecture, in which multiple remote radio heads connected to a centralized base band unit over packet-based eCPRI networks and phase/frequency synchronization is provided by IEEE 1588v2/SyncE. Time and phase synchronization is supported by implementing IEEE1588/SyncE at the remote radio head and centralized base band unit. Higher bandwidth 100 GbE networks are used to backhaul traffic from each base band unit to the core network. Higher performance, more flexible timing solutions are now available that simplify clock generation, distribution and synchronization in LTE-Advanced applications.

Summary

Ethernet is being broadly adopted in data center and wireless networks to enable higher network utilization and lower cost data transmission and to enable new service provider features and services. The transition to packet-based Ethernet networks in these infrastructure applications is driving the need for more flexible, lower jitter timing solutions. Leading timing device vendors are meeting this market need with high-performance clock and oscillator devices based on innovative architectures that enable the utmost in frequency flexibility and ultra-low jitter.